An interesting find today while I was simulating a big chunk of code. The problem occurred in the combinational always block. By rule, we have to put all the inputs to the combinational block in the sensitivity list.

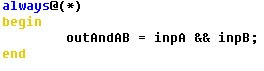

Eg for a simple and gate with input inpA and inpB and output as outAndAB, the coding goes as:-

And if you simulate this design, the code will work fine. But when you move to complex combinational block designs, it is easier and better to assign * in the sensitivity list. In my design I had similar code implemented in three places. While the two worked fine, I got issues in the third implementation. The output didn't get modified when the input changed even though the inputs were there in the sensitivity list. I tried putting the *, which means all, in the sensitivity list and it worked. The tool will optimize the * and put all required signals in the sensitivity list when simulating the code.

After the change the code for the And gate will be :-

So, remember to always put * in the sensitivity list of a combinational block.

No comments :

Post a Comment